#### Materials Sciences and Applications, 2015, 6, 809-817

Published Online September 2015 in SciRes. <a href="http://www.scirp.org/journal/msa">http://www.scirp.org/journal/msa</a> http://dx.doi.org/10.4236/msa.2015.69083

# Effect of Temperature Dependence on Electrical Characterization of *p-n* GaN Diode Fabricated by RF Magnetron Sputtering

## Thi Tran Anh Tuan<sup>1,2</sup>, Dong-Hau Kuo<sup>1\*</sup>, Cheng-Che Li<sup>1</sup>, Guan-Zhang Li<sup>1</sup>

<sup>1</sup>Department of Materials Science and Engineering, National Taiwan University of Science and Technology, Taiwan

<sup>2</sup>School of Basic Sciences, Tra Vinh University, Tra Vinh, Vietnam

Email: \*dhkuo@mail.ntust.edu.tw

Received 21 August 2015; accepted 22 September 2015; published 25 September 2015

Copyright © 2015 by authors and Scientific Research Publishing Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

Open Access

#### **Abstract**

The p-n junction GaN diodes were all fabricated by sputtering technique with cermet targets for p-and n-type GaN and metal targets for electrodes. The interface of these p-n junction GaN diodes examined by high-resolution transition electron microscopy was clear and distinguishable. Lattice images identified the complete dissolution of Mg into the Ga site. At the room temperature, the diode had the turn-on voltage of 2.2 V, the leakage current of  $2.2 \times 10^{-7}$  A, the breakdown voltage of -6 V, the barrier height of 0.56 eV, ideality factor of 5.0 by I (current)-V (voltage) test and 5.2 derived from the Cheungs' method, and series resistance of 560  $\Omega$ . These electrical properties were investigated at different testing temperatures from room temperature to 200°C. The temperature dependence in the I-V characteristics of the p-n diodes can be successfully explained on the basis of thermionic-emission mode.

# **Keywords**

p-n GaN Diode, I-V Measurement, Barrier Height, Leakage Current, Cheungs' Method

#### 1. Introduction

GaN material is one of the important semiconductors for high-power electronics due to its wide band gap characteristics. The nitride-based materials have brought promising future for the application of electronic devices such as metal-oxide-semiconductor field effect transistor (MOSFET) and hetero junction field-effect transistor

\*Corresponding author.

How to cite this paper: Tuan, T.T.A., Kuo, D.-H., Li, C.-C. and Li, G.-Z. (2015) Effect of Temperature Dependence on Electrical Characterization of *p-n* GaN Diode Fabricated by RF Magnetron Sputtering. *Materials Sciences and Applications*, **6**, 809-817. http://dx.doi.org/10.4236/msa.2015.69083

(HJ-FET), Schottky diodes, p-n junction diodes, laser diodes, and light emitting diodes (LEDs). Many researchers have investigated onidentifying carrier recombination centers, defects and impurities, to improve the GaN devices performance [1]-[3]. Such a development from n-GaN to p-GaN is very important for the investigation of Schottky and p-n junction diodes based on GaN films. Generally, the p-n junction diodes will have larger turn-on voltages, lower leakage currents, larger breakdown voltages, and slower switching speeds as compared to Schottky diodes [3]. In the fabrication of p-n junction LED using nitride semiconductor materials, high efficiency and prevention of thermal degradation to get low turn-on voltages of the device are necessary. So, using nitride semiconductor materials to investigate the p-n diodes, the control on the turn-on voltage is the important issue [4]. Moreover, another important requirement for p-n diodes is to have a highly conductive p-type layer with a high holes concentration [5]-[8].

Several groups have put many efforts to explore p-n junction diodes with different approaches. Cao et al. reported the fabrication of  $n^+$ -p junction in GaN by implantation of  $^{29}\text{Si}^+$ . They determined that the breakdown voltage was 13 V at the reverse bias and ideality factor n was ~2 [1]. Lee et al. studied the effect of p-GaN layers on the turn-on voltage of LED. They found that the turn-on voltages at forward bias were in the range of 5.5 - 6.5 V with the incorporation of various amount Mg during growth in p-GaN layer [4]. Gupta et al. investigated the p-n junction based on ZnO and copper phthalocyanineusing pulsed laser deposition and thermal evaporator techniques. After I-V measurement at the room temperature, they reported that the barrier height and ideality factor were  $0.63 \pm 0.02$  eV and  $4.0 \pm 0.3$ , respectively [5]. They also applied Cheungs' and Norde methods to compare the junction parameters. Hwang et al. examined the characteristics of light-emitting diode comprised of p-ZnO/n-GaN hetero junction. The threshold voltage and leakage current were found at 5.4 V and  $2 \times 10^{-4}$  A, respectively [6]. Liu et al. investigated the In GaN-based light-emitting diode with a p-n GaN homojunction. The ideality factor was estimated to be 2.11 at voltage regime of 2 V and barrier height was determined to be 0.77 eV at the room temperature [7]. Park et al. studied the electrical characteristics of a GaN nanorod p-n junction diode patterned on the SiO<sub>2</sub> substrate using e-beamlithography [8]. It was observed that the ideality factor varied from 2460 at 6 K to 13 at 298 K, with a large deviation for the ideal unit. The resistance linearly decreased from 0.05 to 0.0034 M $\Omega$  with the increasing temperature from 100 to 296 K. In the other paper, they reported the electron trapin the GaN nanorod p-n junction grown by molecular-beamepitaxy [9]. Data from the I-V curve showed the turn-on voltage of 7.2 V and breakdown voltage of -9 V at low temperature of 6 K. By increasing the temperature up to 300 K, the turn-on and break down voltages reduced to 0.4 and -0.8 V, respectively. Mohd Yusoff et al. described the growth and characterization of p-n junction diode based on GaN grown on Si (111). Using I-V measurement for the 700°C-annealed GaN grown on AlN/Si (111) substrate, they determined that the extractedideality factors had the range of 15.14 - 19.68, decreasing with an increase in testing temperature (30°C - 104°C) [10]. Zhang et al. fabricated the n-ZnO/p-GaN hetero junction on GaN single crystal substrate with RF magnetron sputtering for ZnO. The threshold voltage was found to be 2.5 V from the I-V data. The current increased rapidly when forward bias was above 2.5 V and it was strongly blocked under reverse bias. Their series resistance  $(R_s)$  of the device was determined to be 102  $\Omega$  from the slope of the curve I/(dI/dV) versus I [11]. All the above-mentioned reports have their GaN films grown by the techniques of metalorganic chemical vapor deposition (MOCVD) and molecular beam epitaxy (MBE). Some of their excellent performances are established on the GaN layers with the epitaxial quality for LEDs [1] [4] [7].

Radio-frequency (RF) reactive sputtering technique has been chosen as a method to grow the p- and n-type GaN layers for the p-n junction GaN diodes. The advantages of using the sputtering technique include lower deposition temperature, low equipment cost, and secure working atmosphere without using the toxic metalorganic precursors and ammonia [12]-[15]. In this study, the electrical I-V characteristics of p-n GaN diodes were determined by the thermionic emission (TE) modeat a wide testing temperature range of 25°C - 200°C.

#### 2. Experimental Procedures

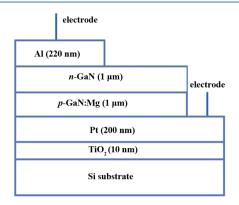

Mg-doped GaN (Mg-GaN) films have been deposited on Si (100) and Pt/TiO<sub>2</sub>/Si substrates at 400°C for 40 min by RF reactive sputtering. The Mg content of (Mg-GaN) cermet targets was 10% [13]. The RF power was kept at 150 W under the mixture of Ar and N<sub>2</sub> gases at a flow rate of 5 sccm for each. The working pressure during sputtering was kept at  $9 \times 10^{-3}$  torr. After depositing *p*-GaN films, the *n*-GaN layers were also grown on Si (100) and *p*-GaN/Pt/TiO<sub>2</sub>/Si substrates at 200°C for 40 min with a Ga/GaN cermet target (**Figure 1**). The process was kept at RF power of 120 W under the similar Ar and N<sub>2</sub> flow rates. Pt and Al deposited by direct-current sputtering were used for the electrodes of *p-n* GaN diode. Aluminum layer was sputtered at 200°C for 30 min with

**Figure 1.** Layers structure of a *p-n* GaN homo junction diode.

a pure Al target. During Al deposition, only Ar gas was used at a flow rate of 5 sccm meanwhile the RF power was kept at 80 W. The detailed experimental procedure for depositing the GaN films can be referred to our previous work [12] [13].

Surface root-mean-square (rms) roughness of Mg-GaN and GaN films was evaluated by atomic force microscopy (AFM, Dimension Icon, Bruker). Before testing TEM images, the FIB system was used to cut samples in *p-n* GaN device. High-resolution transmission electron microscopy (HR-TEM, Tecnai G<sup>2</sup> F20, Philips), operating at 200 keV was used to the determine the SEAD pattern, lattice images of films, and the cross-sectional image of devices. The electrical *I-V* characteristics of *p-n* GaN diodes were determined by using Semiconductor Device Analyzer (Agilent, B1500A) in the temperature range of 25°C - 200°C.

## 3. Results and Discussion

## 3.1. Structural and Surface Morphological Characteristics

Hall effect measurement (HMS-2000, Ecopia) was conducted for the electron concentration ( $N_d$ ), hole concentration ( $N_p$ ), and carrier mobility ( $\mu$ ) of n- and p-GaN films at the room temperature. As a result, they were found to be  $N_d = 5.8 \times 10^{17}$  cm<sup>-3</sup> and  $\mu = 11$  cm<sup>2</sup>/Vs for n-GaN film and  $N_p = 2.1 \times 10^{17}$  cm<sup>-3</sup> and  $\mu = 26$  cm<sup>2</sup>/Vs for p-GaN films. In our previous study on materials development, the band gap  $E_g$  values of n-GaN deposited at  $200^{\circ}$ C and p-GaN deposited at  $400^{\circ}$ C were found to be 2.99 and 2.96 eV, respectively [12] [13].

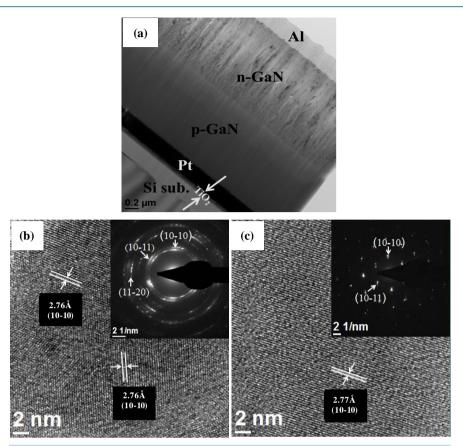

The layers structure of p-n GaN homo junction diode is shown in the **Figure 1**. The cross-sectional TEM image of the p-n GaN diode structure is shown in **Figure 2(a)**. Each layer of the diode exhibited good adhesion. The interface between p- and n-GaN layers was crack- and pore-free. The interface between n- and p-GaN is clearly distinguished, which indicates interfacial diffusion is minimized because of depositing firstly p-GaN at higher temperature of 400°C followed by n-GaN at lower temperature of 200°C. The thicknesses of Al and Pt electrodes were 200 and 220 nm, respectively. The Pt/TiO $_2$ /Si combination has been popularly used for the study of non-volatile memory. The thicknessof n- and p-GaN layers was found to be 1  $\mu$ m. As an original work, the thickness effect on the diode performance needs further investigations.

The high-resolution (HR) TEM lattice images of films are presented in **Figure 2(b)** for n-GaN and **Figure 2(c)** for p-GaN. The insets show the selected area electron diffraction (SAED) patterns. The n- and p-GaN phases were clean and had no second phases. The lattice images provide important evidence to support the homogeneity of the n- and p-GaN deposited by reactive sputtering. It is especially important for p-GaN, because this information can guarantee the complete dissolution of Mg dopant into the Ga lattice site to form the complete solid solution without phase segregation. The Mg solubility in GaN is well known for using the MOCVD technique. Our lattice images indicate that the sputtering kinetic energy is strong enough to dissolve Mg into the Ga lattice. For the n-GaN layer, the measured d-space value was 2.76 Å, which corresponded to the (1010) crystalline plane. Other crystalline plane such as (1011) and (1120) could also be observed from the SAED pattern. For the p-GaN layer, the measured d-space value had a bigger value of 2.77 Å due to the lattice expansion by using the bigger Mg dopant of 0.66 Å to substitute the smaller Ga of 0.62 Å. The HR lattice image of p-GaN exhibited similar crystalline (1010) plane. However, the (1011) plane still showed in SAED pattern. Both of n- and p-GaN films show the polycrystalline nature. The n-GaN has a ring diffraction pattern contributed from different

**Figure 2.** TEM micrographs of (a) p-n GaN diode structure, (b) n-GaN layer, and (c) p-GaN layer.

crystalline planes. The p-GaN shows the dotted pattern, which indicates the p-GaN has the tendency to become single crystal-like. In addition, the XRD results from our previous indicate that full-width at half-maximum (FWHM) at  $(10\overline{1}1)$  is 0.30 for pure n-GaN and 0.25 for p-Mg-doped GaN at 10% [13]. The addition of 10% Mg improved slightly the structure of GaN. The instead of excess (~15%) and less (~5%) Mg-doped GaN films, the FWHM of  $(10\overline{1}1)$  was increased to 0.30 and 0.34, respectively. The TEM characterization supports with the evidence that Mg doping can improve the crystallinity of the growing p-GaN films.

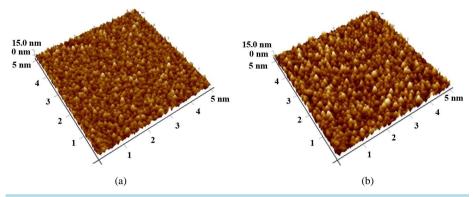

Surface topographies of both GaN films were analyzed by AFM, as shown in Figure 3(a) and Figure 3(b), respectively. The root-mean-square (rms) roughness values of n- and p-GaN were found to be 2.42 and 3.12 nm, respectively. The grains become larger and the surface rougher due to the Mg doping into the GaN films. The surface roughness of p-GaN can be attributed to the disturbance of growth kinetics by the Mg dopant or a difference in atomic size between Ga and Mg, which made the lattice distortion and dislocation generation.

## 3.2. Current-Voltage (I-V) Characteristics

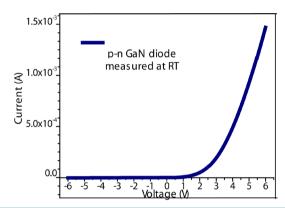

**Figure 4** shows the plot of the *I-V* characteristics of p-n GaN diode at the room temperature. The leakage current of p-n GaN diode was  $2.2 \times 10^{-7}$  A at -1 V. The turn-on voltage was found at  $\sim 2.2$  V for the forward bias, and the breakdown voltage was determined above -6 V.

The forward and reverse I-V characteristicofa p-n GaN diode was also determined at the different testing temperatures. The electrical characteristics can be generally evaluated by using an equation based on a well-known standard thermionic-emission (TE) relation for electron transport from a metal-semiconductor contact (for qV > 3 kT) [5] [14] [16]. It can be given as below

$$I = I_0 \left[ \exp \frac{qV}{nkT} V - 1 \right] \tag{1}$$

Figure 3. AFM topographies of (a) n-GaN filmdeposited at 200°C and (b) p-GaN filmdeposited at 400°C.

**Figure 4.** Electrical properties of *p-n* GaN homo junction diode measured at the room temperature (RT).

where V is applied voltage, T the experiment temperature in Kelvin, n ideality factor,  $I_0$  saturation current, q the electronic charge, and k the Boltzmann constant. The saturation current is expressed by

$$I_0 = AA^*T^2 \exp\left(-\frac{q\phi_B}{kT}\right) \tag{2}$$

where  $A^*$  is the effective Richardson constant, A the diode area, and  $\phi_B$  the barrier height. In the present work, the p-n GaN diode has a square shape and its area was measured to be 1 mm<sup>2</sup>. The theoretical value of  $A^*$  was found to be 26.4 Acm<sup>-2</sup>/K<sup>-2</sup>, based on the effective electron mass ( $m^* = 0.22 \ m_e$ ) for GaN [16]-[19]. The plot of ln I versus V, based upon Equation (1), can be used to derive the saturation current, which can be obtained by extrapolated the straight line of the linear region of the semilog plot to zero applied voltage. The barrier height of the p-n GaN diode is defined as

$$\phi_B = \frac{kT}{q} \ln \left( \frac{AA^*T^2}{I_0} \right) \tag{3}$$

In addition, the calculation of the ideality factor n is based upon the pure TE mode. It can be obtained from the slope of the linear region of  $\ln I-V$  characteristics under the forward bias. It is given by [5] [16]-[19]

$$n = \frac{q}{kT} \left( \frac{\mathrm{d}V}{\mathrm{d}\ln I} \right) \tag{4}$$

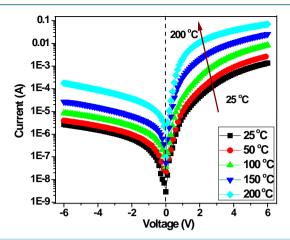

**Figure 5** shows that the logarithmic plot of *I-V* characteristics as a function of testing temperature (25°C - 200°C). It is noted that the leakage current at the reverse bias of -1 V goes up from  $2.2 \times 10^{-7}$  A at RT to  $1.7 \times 10^{-5}$  A at 200°C. The barrier heights, based on equation (2) and (3), were found to increase from 0.56 eV at 25°C

**Figure 5.** The forward and reverse current-voltage characteristics of a *p-n* GaN diodein the testing temperature range of 25°C - 200°C.

to 0.69 eV at 200°C. By using Equation (4), the ideality factor n decreased with the increase in the testing temperature, dropped from 5.0 at 25°C to 2.5 at 200°C. These achieved parameters for the diode with all layers made by sputtering are consistent with the reported values in some previous papers for p-n junction diodes with GaN made by MOCVD [5] [9].

## 3.3. Calculations the Series Resistance $R_s$ and Ideality Factor n

The series resistance  $R_s$  and the ideality factor n are very important parameters. The I-V characteristics deviate considerably with the change in ideality factor n due to the effect of series resistance  $R_s$ . The series resistance  $R_s$  and ideality factor n of a p-n diodes can be determined by using the Cheungs' method [20], which is defined as below

$$\frac{\mathrm{d}V}{\mathrm{d}(\ln I)} = \frac{nkT}{q} + IR_{S} \tag{5}$$

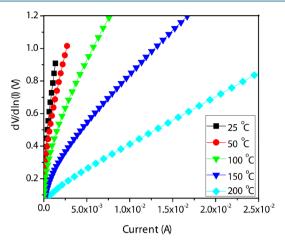

As can be seen **Figure 6**, the plot of dV/d (lnI) versus I will be linear (based on Equation (5)). The slopes will give the values of series resistance  $R_s$  and the intercepts will give the values of ideality factor n [5] [15] [18] [20]. **Table 1** also provides the results from a detailed calculation of the series resistances  $R_s$  and ideality factor n by the Cheungs' method.

#### 3.4. Discussion

**Table 1** shows a comparison of data derived from the *I-V* data for the all sputtering-made *p-n* GaN diode. It is noted that the ideality factor *n* decreases whereas the barrier increases with the increase in the testing temperature. This result can be attributed to the combination of the low and high barrier heights of diodes with the *I-V* behavior in the standard TE mode. At the room temperature, the flow of the electron transport across the metal-semiconductor interface of devices is able to overcome the lower barriers. Therefore, the current transport will be determined by electrons flowing through the path of lower barrier height and a larger ideality factor. When the testing temperature increases, more and more electrons will have sufficient energy to transcend the higher barrier. As a result, the dominant barrier height will increase with increasing the testing temperature [17]. Other reasons are the inhomogeneous thickness of films and non-uniformity of the interfacial charges to lead to the increase in ideality factor and the decrease in the barrier height for testing at lower temperatures. In addition, the increase in the carrier concentration of GaN layers and the decrease in the parasitic resistances found at the higher testing temperature also have caused the rise of barrier height and the fall of ideality factor [21].

Similar results were also determined by Hsueh *et al.* [21]. They investigated the temperature dependence of the current-voltage characteristics of n-Mg<sub>x</sub>Zn<sub>1-x</sub>O/p-GaN hetero-junction diodes. They concluded that at asubstrate temperature of 25°C there was the lowest leakage current at the reverse bias. Furthermore, the extracted ideality factors n were in the range of 3.86 - 7.00, decreasing with an increase in the testing temperature (25°C - 125°C).

Figure 6. Plot of dV/dln(I) versus I for p-n GaN diode in the temperature range of  $25^{\circ}$ C -  $200^{\circ}$ C.

**Table 1.** The parameters calculated from electrical characteristics of a *p-n* GaN diode as a function of testing temperature.

| Temp (°C) | Leakage current (A) at −1 V | Barrier height     | From I-V | Cheungs' function dV/dln(I) vs I |     |

|-----------|-----------------------------|--------------------|----------|----------------------------------|-----|

|           |                             | $\phi_{_{B}}$ (eV) | N        | $Rs(\Omega)$                     | n   |

| 25        | $2.2 \times 10^{-7}$        | 0.56               | 5.0      | 560                              | 5.2 |

| 50        | $3.8 \times 10^{-7}$        | 0.59               | 4.6      | 362                              | 4.9 |

| 100       | $1.1 \times 10^{-6}$        | 0.63               | 3.7      | 165                              | 4.0 |

| 150       | $3.1 \times 10^{-6}$        | 0.67               | 3.1      | 78                               | 3.4 |

| 200       | $1.7 \times 10^{-5}$        | 0.69               | 2.5      | 38                               | 2.7 |

In the other paper, they also investigated the *I-V* characteristics at different testing temperatures for Al-doped  $Mg_xZn_{1-x}O/AlGaN$  junction diodes with Mg-ZnO made by RF sputtering on the MOCVD-grown AlGaN. The extracted ideality factors were found in the range of 5.04 - 15.90, decreasing as the testing temperature increased from 25°C to 125°C [22]. Mohd Yusoff *et al.* described the growth and characterization of *p-n* junction diode based on GaN grown on Si (111) [10]. The leakage current was found  $1.32 \times 10^{-6}$  at the room temperature. The ideality factors *n* had the range of 15.14 - 19.68, decreasing with an increase in testing temperature (30°C - 104°C). Chen *et al.* studied the current rectification in a single GaN nanowire with a well-defined *p-n* junction [23]. Their ideality factor was calculated in the range of 5.5 - 6.5. The higher ideality factor was also obtained after testing at lower temperatures.

It is observed that there is a small difference between the values of ideality factor obtained from the  $\ln I - V$  plot at forward bias and from the  $dV/d(\ln I) - I$  plot. This difference could be due to the presence of series resistance, interface states, and the voltage drop across the interfacial layer [21]-[23]. A good diode is expected to have small temperature dependence in ideality factor. So, the observed high ideality factor could be due to several reasons such as accelerated recombination of electrons and holes in depletion region, the presence of interfacial layer, and the imperfections which may be due to the presence of crystalline and amorphous regions [5] [6].

From **Table 1**, there is also a clear trend of decreasingtheseries resistances  $R_s$  with a rise in the testing temperature. The  $R_s$  values were observed to drop from 560  $\Omega$  at 25°C to 38  $\Omega$  at 200°C. The fall in  $R_s$  for p-n GaN diode tested a higher temperature indicates that the diode has smaller ideality factor, more free electrons leading to the high current, and smaller series resistance in the forward bias.

#### 4. Conclusion

p-n GaN diodes have been successfully fabricated only by using the cost-effective magnetron sputtering. The p-n diode has a good homo-junction with a distinguishable interface and free of voids and cracking. The leakage

current, turn-on voltage, ideality factor, and breakdown voltage of the diode device, obtained from I-V measurements, were found to be  $2.2 \times 10^{-7}$  A, 2.2 V, 5.0, and -6 V, respectively, at room temperature. With increasing the testing temperature, the barrier height increased from 0.56 eV at  $25^{\circ}$ C to 0.69 eV at  $200^{\circ}$ C; the ideality factor decreased from 5.0 to 2.5 for I-V tests and from 5.2 to 2.7 from Cheungs' method; and the series resistance decreased from  $560~\Omega$  to  $38~\Omega$ . It is observed that the ideality factor and series resistance decrease whereas the barrier height increases as the testing temperature increases.

## **Acknowledgements**

This work was supported by the Ministry of Science and Technology of Taiwan under grant numbers MOST 104-2623-E-011-003-ET and MOST 104-2811-E-011-005.

#### References

- [1] Cao, J., Laroche, J.A., Ren, F., Peaton, S.J., Lothian, J.A., Singh, R.K., Wilson, R.G., Guo, H.J. and Pennycook, S.J. (1999) Implanted p-n Junctions in GaN. *Solid-State Electron*, 43, 1235-1238. http://dx.doi.org/10.1016/S0038-1101(99)00012-X

- [2] Lee, M.L., Sheu, J.K., Yeh, L.S., Tsai, M.S., Kao, C.J., Tun, C.J., Chang, S.J. and Chi, G.C. (2002) GaN p-n Junction Diode Formed by Si Ion Implantation into p-GaN. *Solid-State Electron*, 46, 2179-2183. <a href="http://dx.doi.org/10.1016/S0038-1101(02)00224-1">http://dx.doi.org/10.1016/S0038-1101(02)00224-1</a>

- [3] Baik, K.H., Irokawa, Y., Ren, F., Pearton, S.J., Park, S.S. and Park, Y.J. (2003) Temperature Dependence of Forward Current Characteristics of GaN Junction and Schottky Rectifiers. *Solid-State Electron*, 47, 1533-1538. http://dx.doi.org/10.1016/S0038-1101(03)00071-6

- [4] Lee, C.R., Yeon, J.M., Choi, D.K. and Ahn, H.K. (2001) The Effect of p-GaN: Mg Layers on the Turn-On Voltage of p-n Junction LED. *Journal of Crystal Growth*, **222**, 459-464. <a href="http://dx.doi.org/10.1016/S0022-0248(00)00930-1">http://dx.doi.org/10.1016/S0022-0248(00)00930-1</a>

- [5] Gupta, R.K., Yakuphanoglu, F., Ghosh, K. and Kahol, P.K. (2011) Fabrication and Characterization of p-n Junctions Based on ZnO and CuPc. *Microelectronic Engineering*, **88**, 3067-3069. http://dx.doi.org/10.1016/j.mee.2011.05.023

- [6] Hwang, K., Kang, S.H., Lim, J.H., Yang, E.J., Oh, J.Y. and Park, S.J. (2005) p-ZnO/n-GaN Heterostructure ZnO Light-Emitting Diodes. Applied Physics Letters, 86, Article ID: 222101. http://dx.doi.org/10.1063/1.1940736

- [7] Liu, Y.J., Guo, D.F., Chua, K.F., Cheng, S.Y., Liou, J.K., Chen, L.Y., Tsai, T.H., Huang, C.C., Chen, T.Y., Hsua, C.S., Tsai, T.Y. and Liu, W.C. (2011) Improved Current-Spreading Performance of an InGaN-Based Light-Emitting Diode with a Clear p-GaN/n-GaN Barrier Junction. *Displays*, 32, 330-333. <a href="http://dx.doi.org/10.1016/j.displa.2011.04.004">http://dx.doi.org/10.1016/j.displa.2011.04.004</a>

- [8] Park, Y.S., Park, C.M., Lee, J.W., Cho, H.Y., Kang, T.W., Yoo, K.H., Son, M.S. and Han, M. (2008) Electrical Transport Properties of a Nanorod GaN p-n Homo Junction Grown by Molecular-Beam Epitaxy. *Journal of Applied Physics*, **103**, Article ID: 066107. <a href="http://dx.doi.org/10.1063/1.2896636">http://dx.doi.org/10.1063/1.2896636</a>

- [9] Park, Y.S., Park, C.M., Park, C.J., Cho, H.J., Lee, S.J., Kang, T.W., Lee, S.H., Oh, J.E., Yoo, K.H. and Son, M.S. (2006) Electron Trap Level in a GaN Nanorod p-n Junction Grown by Molecular-Beam Epitaxy. *Applied Physics Letters*, 88, Article ID: 192104. http://dx.doi.org/10.1063/1.2203735

- [10] Mohd Yusoff, M.Z., Hassan, Z., Ahmed, N.M., Hassan, H., Abdullah, M.J. and Rashid, M. (2013) pn-Junction Photodiode Based on GaN Grown on Si (111) by Plasma-Assisted Molecular Beam Epitaxy. *Materials Science in Semicon*ductor Processing, 16, 1859-1864. http://dx.doi.org/10.1016/j.mssp.2013.07.015

- [11] Shen, Y.W., Chen, X., Yan, X.Q., Yi, F., Bai, Z.M., Zheng, X., Lin, P. and Zhang, Y. (2014) Low-Voltage Blue Light Emission from n-ZnO/p-GaN Heterojunction Formed by RF Magnetron Sputtering Method. *Current Applied Physics*, 14, 345-348. http://dx.doi.org/10.1016/j.cap.2013.12.011

- [12] Li, C.C. and Kuo, D.H. (2014) Effects of Growth Temperature on Electrical and Structural Properties of Sputtered GaN Films with a Cermet Target. *Journal of Materials Science: Materials in Electronics*, 25, 1404-1409. <a href="http://dx.doi.org/10.1007/s10854-014-1742-4">http://dx.doi.org/10.1007/s10854-014-1742-4</a>

- [13] Li, C.C. and Kuo, D.H. (2014) Material and Technology Developments of the Totally Sputtering-Made p/n GaN Diodes for Cost-Effective Power Electronics. *Journal of Materials Science: Materials in Electronics*, 25, 1942-1948. http://dx.doi.org/10.1007/s10854-014-1826-1

- [14] Tuan, T.T.A., Kuo, D.H., Lin, K.F. and Li, G.Z. (2015) Temperature Dependence of Electrical Characteristics of n-In<sub>x</sub>Ga<sub>1-x</sub>N/p-Si Hetero-Junctions Made Totally by RF Magnetron Sputtering. Thin Solid Films, 589, 182-187. http://dx.doi.org/10.1016/j.tsf.2015.05.018

- [15] Tuan, T.T.A. and Kuo, D.H. (2015) Characteristics of RF Reactive Sputter-Deposited Pt/SiO<sub>2</sub>/n-InGaN MOS Schottky Diodes. *Materials Science in Semiconductor Processing*, **30**, 314-320. http://dx.doi.org/10.1016/j.mssp.2014.10.021

- [16] Ravinandan, M., Rao, P.K. and Reddy, V.R. (2008) Temperature Dependence of Current-Voltage (*I-V*) Characteristics of Pt/Au Schottky Contacts on N-Type GaN. *Journal of Optoelectronics and Advanced Materials*, **10**, 2787-2792.

- [17] Kumar, A., Vinayak, S. and Singh, R. (2013) Micro-Structural and Temperature Dependent Electrical Characterization of Ni/GaN Schottky Barrier Diodes. *Current Applied Physics*, 13, 1137-1142. <a href="http://dx.doi.org/10.1016/j.cap.2013.03.009">http://dx.doi.org/10.1016/j.cap.2013.03.009</a>

- [18] Kumar, A., Arafin, S., Amann, M.C. and Kumar, R.S. (2013) Temperature Dependence of Electrical Characteristics of Pt/GaN Schottky Diode Fabricated by UHV E-Beam Evaporation. *Nanoscale Research Letters*, 8, 481. <a href="http://dx.doi.org/10.1186/1556-276X-8-481">http://dx.doi.org/10.1186/1556-276X-8-481</a>

- [19] Reddy, N.N., Reddy, V.R. and Choi, C.J. (2011) Influence of Rapid Thermal Annealing Effect on Electrical and Structural Properties of Pd/Ru Schottky Contacts to N-Type GaN. *Materials Chemistry and Physics*, 130, 1000-1006. http://dx.doi.org/10.1016/j.matchemphys.2011.08.026

- [20] Cheung, S.K. and Cheung, N.W. (1985) Extraction of Schottky Diode Parameters from Forward Current-Voltage Characteristics. Applied Physics Letters, 49, 85. <a href="http://dx.doi.org/10.1063/1.97359">http://dx.doi.org/10.1063/1.97359</a>

- [21] Hsueh, K.P. (2011) Temperature Dependent Current-Voltage Characteristics of n-Mg<sub>x</sub>Zn<sub>1-x</sub>O/p-GaN Junction Diodes. Microelectronic Engineering, 88, 1016-1018. <a href="http://dx.doi.org/10.1016/j.mee.2011.01.068">http://dx.doi.org/10.1016/j.mee.2011.01.068</a>

- [22] Hsueh, K.P., Cheng, P.W., Lin, W.Y., Chiu, H.C., Wang, H.C., Sheu, J.K. and Yeh, Y.H. (2014) Temperature-Dependent Current-Voltage Characteristics of Al-Doped Mg<sub>x</sub>Zn<sub>1-x</sub>O/AlGaN n-p Junction Diodes. ECS Journal of Solid State Science and Technology, 3, Q65-Q68. <a href="http://dx.doi.org/10.1149/2.026404jss">http://dx.doi.org/10.1149/2.026404jss</a>

- [23] Cheng, G.S., Kolmakov, A., Zhang, Y.X., Moskovits, M., Munden, R., Reed, M.A., Wang, G.M., Moses, D. and Zhang, J.P. (2003) Current Rectification in a Single GaN Nanowire with a Well-Defined *p-n* Junction. *Applied Physics Letters*, **83**, 1578. <a href="http://dx.doi.org/10.1063/1.1604190">http://dx.doi.org/10.1063/1.1604190</a>